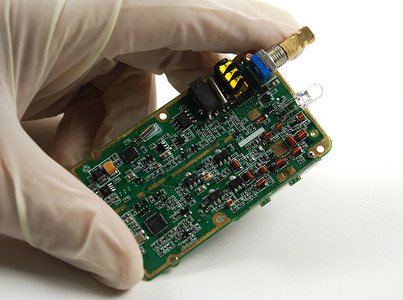

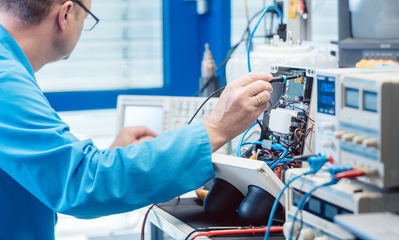

在聯(lián)合微電子中心(UMC)的潔凈實(shí)驗(yàn)室里,工程師們正在進(jìn)行一場(chǎng)精密而嚴(yán)謹(jǐn)?shù)墓に嚋y(cè)試。這一場(chǎng)景不僅是電子工程領(lǐng)域日常研發(fā)的縮影,更是現(xiàn)代半導(dǎo)體技術(shù)不斷突破的核心環(huán)節(jié)。

實(shí)驗(yàn)室環(huán)境嚴(yán)格控制,溫度、濕度和空氣潔凈度都維持在極高標(biāo)準(zhǔn)。工程師們身著全套防靜電無(wú)塵服,通過(guò)顯微鏡和各類精密儀器,對(duì)新一代芯片的制造工藝進(jìn)行反復(fù)驗(yàn)證與優(yōu)化。工藝測(cè)試涉及光刻、蝕刻、薄膜沉積、離子注入等多個(gè)關(guān)鍵步驟,每一個(gè)參數(shù)的微小調(diào)整都可能直接影響最終芯片的性能、功耗和可靠性。

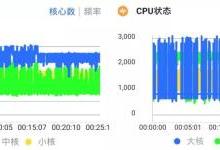

在電子工程的前沿,此類測(cè)試的目標(biāo)往往是提升制程節(jié)點(diǎn)的成熟度,例如從28納米向更先進(jìn)的14納米或7納米工藝邁進(jìn)。工程師需要分析測(cè)試晶圓上的電性數(shù)據(jù),排查缺陷成因,并與設(shè)計(jì)團(tuán)隊(duì)、設(shè)備供應(yīng)商緊密協(xié)作,通過(guò)迭代實(shí)驗(yàn)找到最佳工藝窗口。這不僅需要深厚的半導(dǎo)體物理和材料科學(xué)知識(shí),更要求工程師具備極強(qiáng)的數(shù)據(jù)分析能力和解決問(wèn)題的系統(tǒng)性思維。

聯(lián)合微電子中心作為全球重要的晶圓代工廠商,其實(shí)驗(yàn)室的工藝測(cè)試工作直接關(guān)系到客戶芯片產(chǎn)品的成功量產(chǎn)。每一次成功的測(cè)試,都意味著技術(shù)在功耗、性能、面積和成本(PPAC)方面取得了新的平衡,為人工智能、5G通信、物聯(lián)網(wǎng)和汽車電子等應(yīng)用領(lǐng)域注入更強(qiáng)大的硬件動(dòng)力。

因此,實(shí)驗(yàn)室里那些專注的身影,代表的不僅是工程師個(gè)人的專業(yè)素養(yǎng),更是整個(gè)電子工程產(chǎn)業(yè)追求極致、推動(dòng)數(shù)字世界不斷向前發(fā)展的生動(dòng)寫照。工藝測(cè)試,這一在微觀世界里進(jìn)行的精密舞蹈,正持續(xù)塑造著我們宏觀的科技未來(lái)。